iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version : V1.1

# MQ6812/MQ6821/MQ6822 Datasheet V1.1

iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

| 1.   | Char    | nge History                                    | 6  |

|------|---------|------------------------------------------------|----|

| 2.   | Prod    | uct Overview                                   | 7  |

|      | 2.1     | Features                                       | 7  |

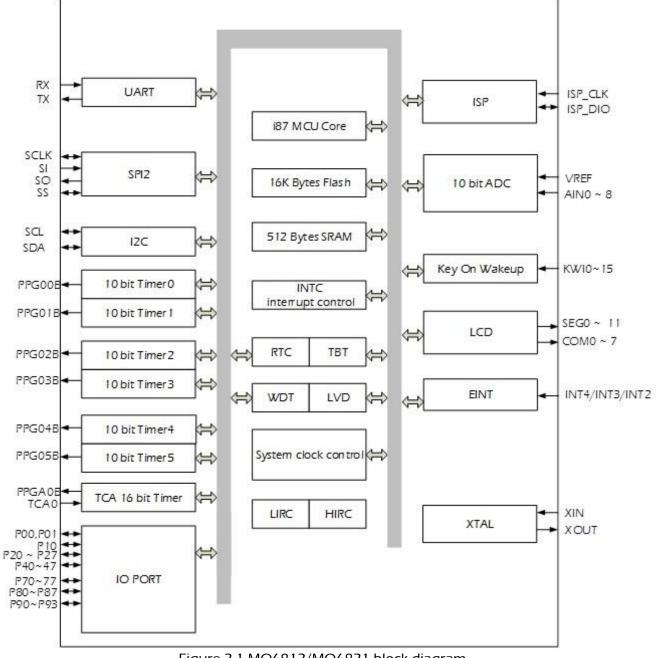

|      | 2.2     | Block Diagram                                  | 11 |

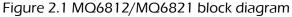

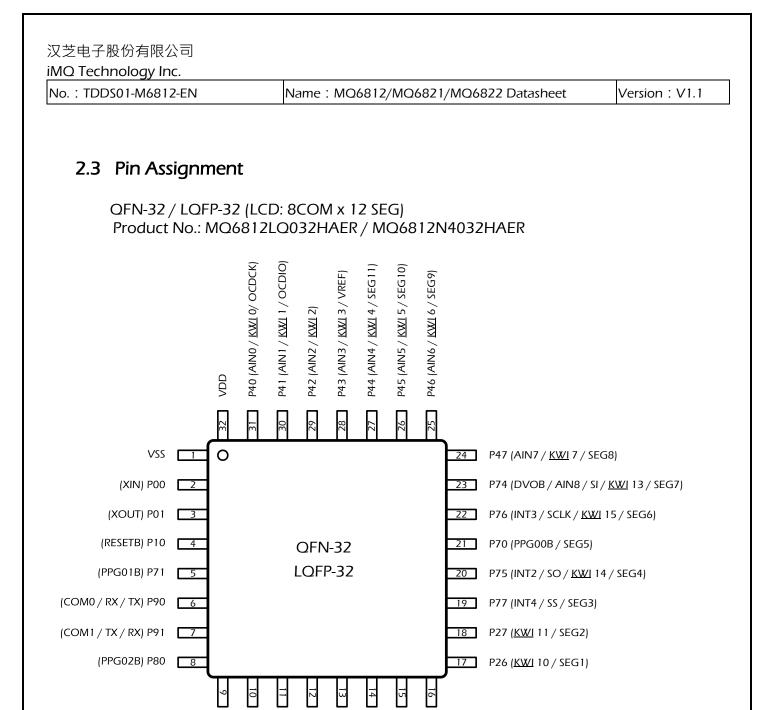

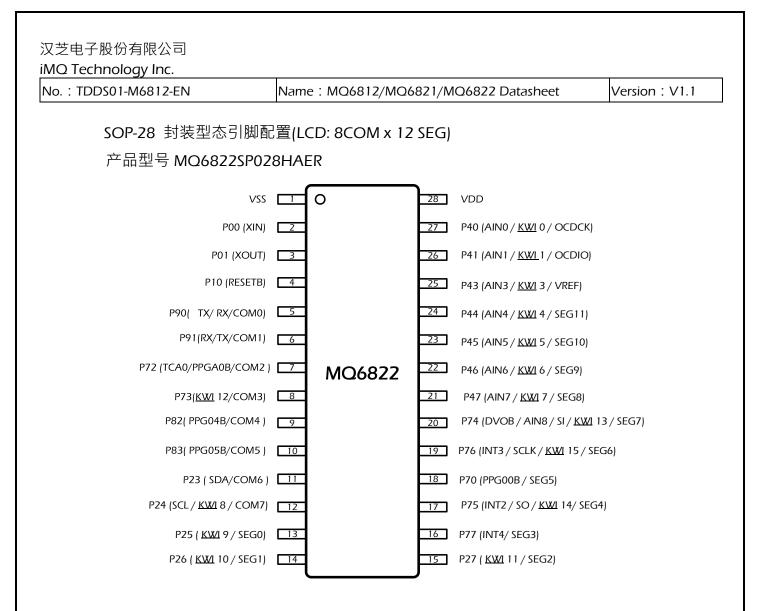

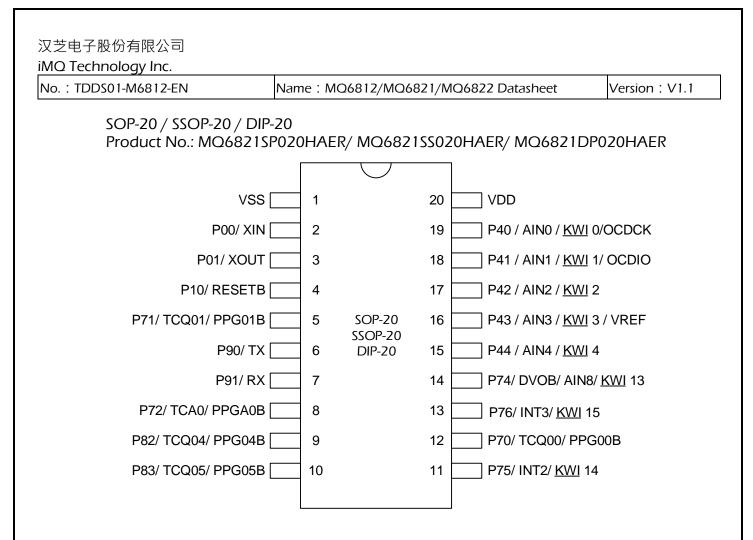

|      | 2.3     | Pin Assignment                                 | 12 |

| З.   | Elect   | ronic Characteristics                          | 22 |

|      | 3.1     | Absolute Maximum Ratings                       | 22 |

|      | 3.2     | Operation Conditions                           | 23 |

|      | 3.3     | DC Characteristics                             | 23 |

|      | 3.4     | AD Conversion Characteristics                  | 25 |

|      | 3.5     | Flash Characteristics                          | 26 |

|      | 3.6     | LCD Characteristics                            | 26 |

| 4.   | Cent    | ral Processing Unit (CPU)                      | 27 |

|      | 4.1     | General Concept                                | 27 |

|      | 4.2     | Addressing Space                               | 27 |

|      | 4.3     | Operation Modes                                | 30 |

|      | 4.4     | Stack Area and Stack Pointer                   | 43 |

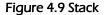

|      | 4.5     | Program Counter (PC)                           | 44 |

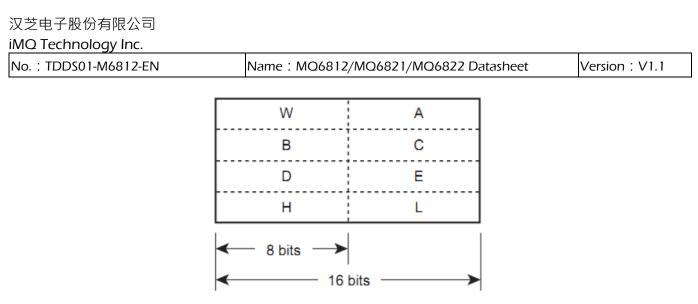

|      | 4.6     | General-Purpose Register                       | 45 |

|      | 4.7     | Program Status Word (PSW)                      | 47 |

|      | 4.8     | Low Power Consumption Function for Peripherals | 50 |

|      | 4.9     | Key-on Wakeup (KWU)                            | 52 |

| 5. I | Reset I | -unction                                       | 56 |

|      | 5.1     | Reset Control Circuit                          | 56 |

|      | 5.2     | Power-on Reset Circuit                         | 64 |

|      | 5.3     | Voltage Detection Circuit                      | 65 |

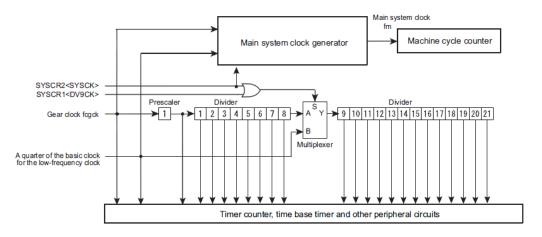

| 6. 9 | System  | n Clock Controller                             | 72 |

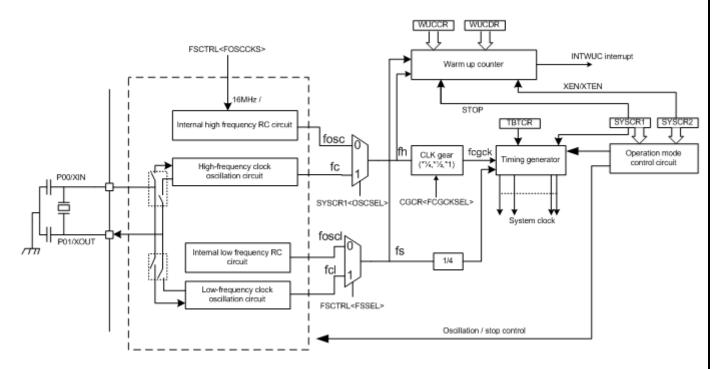

|      | 6.1     | Configuration                                  | 72 |

|      | 6.2 (   | Control                                        | 73 |

|      | 6.3 F   | Function                                       | 76 |

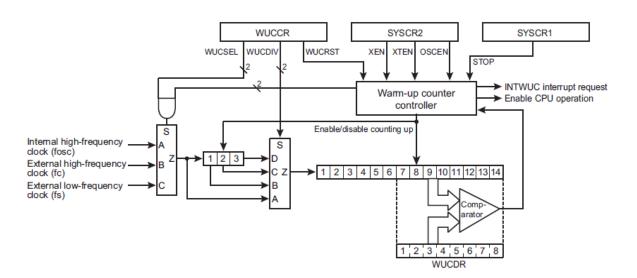

|      | 6.4     | Warm-up Counter                                | 79 |

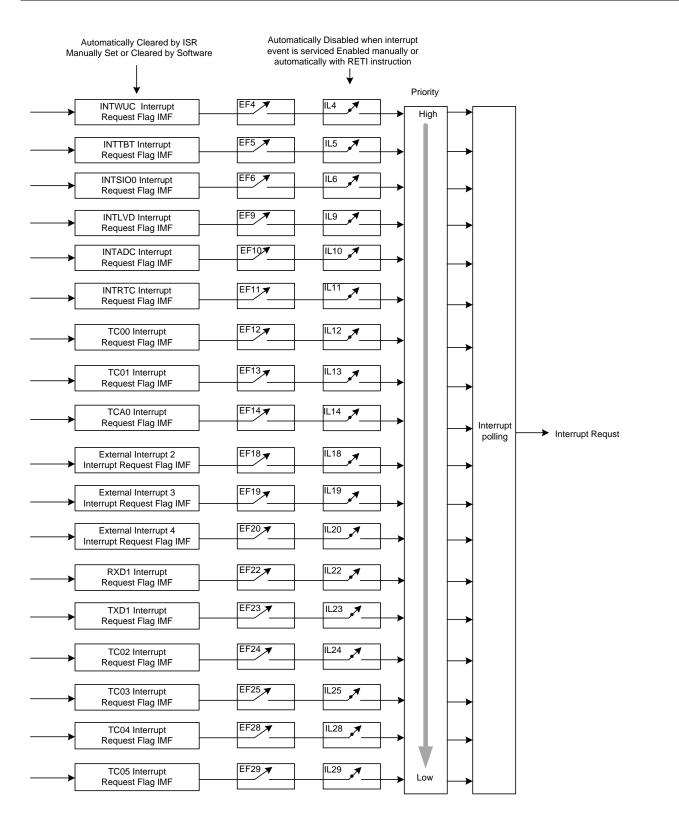

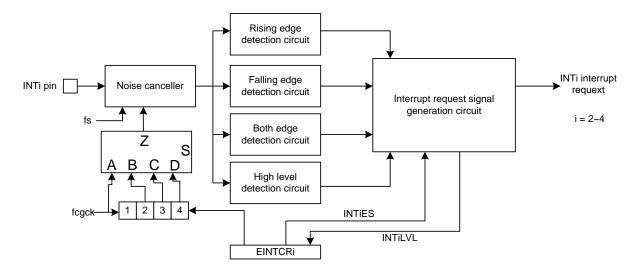

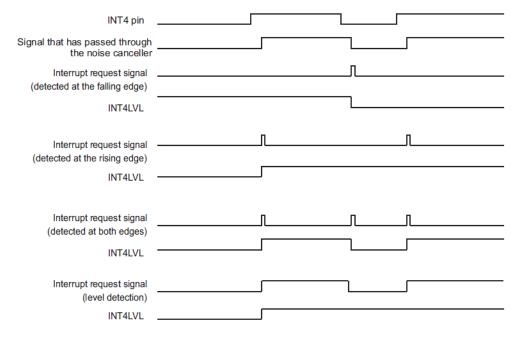

汉芝电子股份有限公司 iMQ Technology Inc. Version: V1.1 No. : TDDS01-M6812-EN Name : MQ6812/MQ6821/MQ6822 Datasheet 7.1 Interrupts Latches (IL29 to IL3)......85 Interrupt Enable Register (EIR)......85 7.2 7.3 Interrupt Master Enable Flag (IMF) ......85 7.4 Individual Interrupt Enable Flag (EF29 to EF4)......86 7.5 8.1 8.2 8.3 9.1 9.2 9.3 9.4 9.5 9.6 Analog Input Voltage and AD Conversion Result...... 122 Precautions about the AD Converter ...... 123 9.7 10.1 Watchdog Timer/ Watchdog Timer2 (WDT/WDT2)......124 10.5 10-bit Timer Counters ...... 139

iMQ Technology Inc. No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

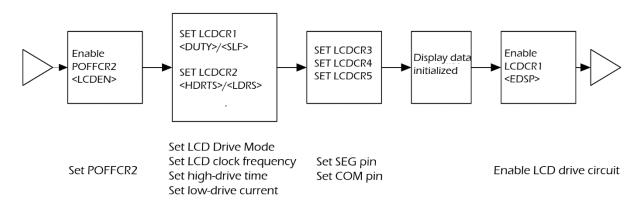

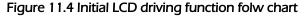

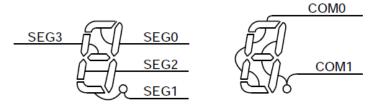

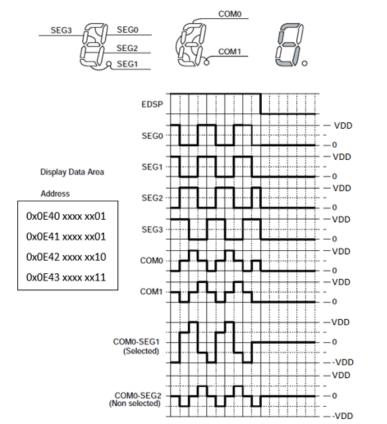

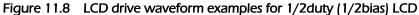

| 11.6 The Example of LCD                                               | 188 |

|-----------------------------------------------------------------------|-----|

| 12.Asynchronous Serial Interface (UART)                               | 192 |

| 12.1 Control                                                          | 192 |

| 12.2 Low Power Consumption Function                                   | 196 |

| 12.3 Protection of UART1CR1 and UART1CR2 Registers from Being Changed | 196 |

| 12.4 Activation of STOP, IDLE0 or SLEEP0 Mode                         | 197 |

| 12.5 Transfer Data Format                                             | 197 |

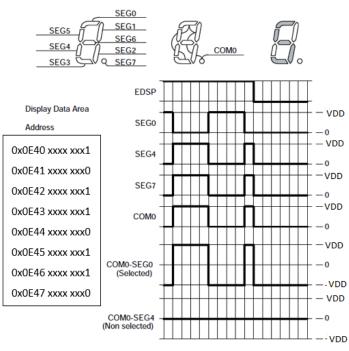

| 12.6 Infrared Data Format Transfer Mode                               | 198 |

| 12.7 Transfer Baud Rate                                               | 199 |

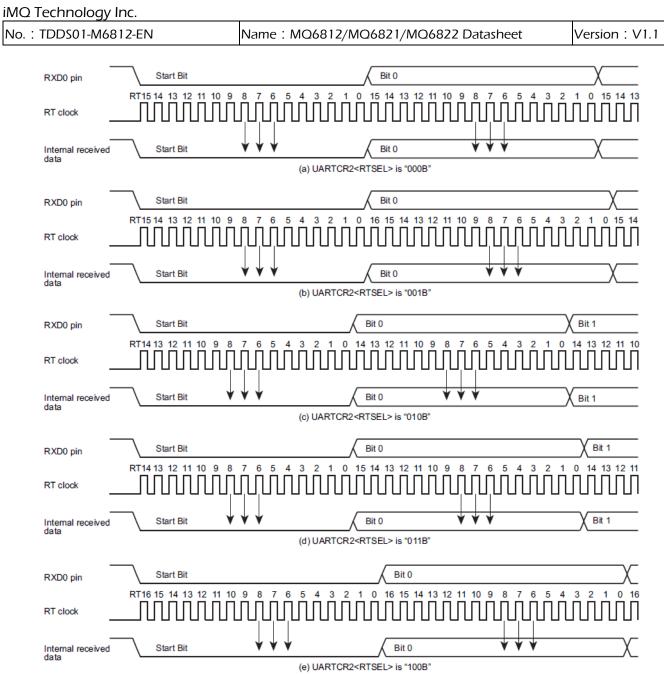

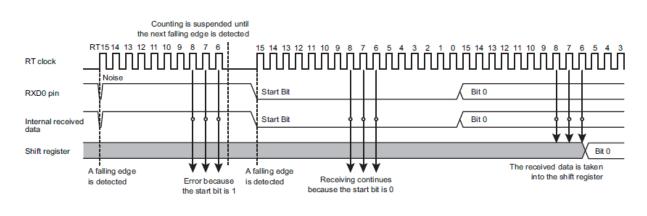

| 12.8 Data Sampling Method                                             | 201 |

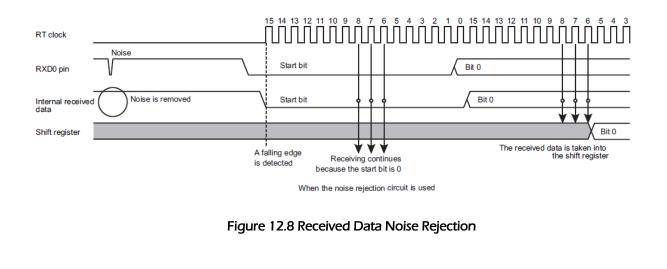

| 12.9 Received Data Noise Rejection                                    | 203 |

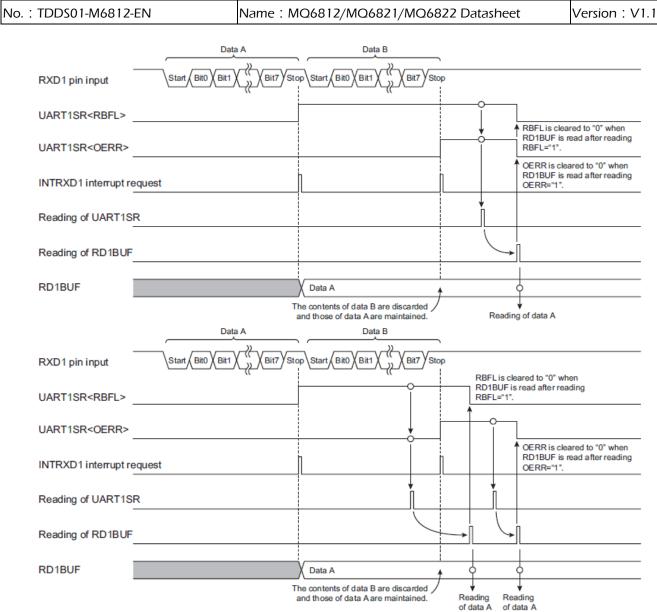

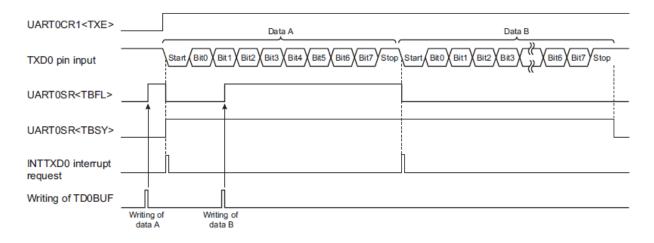

| 12.10 Transmit/Receive Operation                                      | 204 |

| 12.11 Transmit/Receive Operation                                      | 205 |

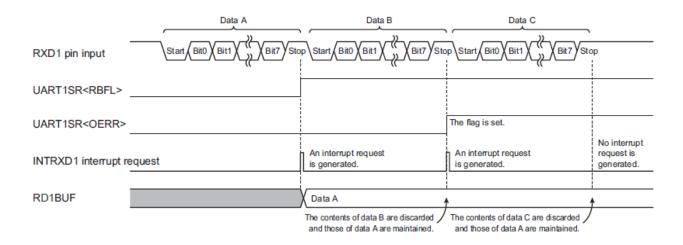

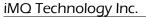

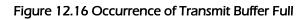

| 12.12 Receiving Process                                               | 211 |

| 13. Flash Memory                                                      | 214 |

| 13.1 Flash Memory Control                                             | 214 |

| 13.2 Flash Memory Functions                                           | 215 |

| 13.3 Command Sequence                                                 | 216 |

| 13.4 Access to the Flash Memory Area                                  | 217 |

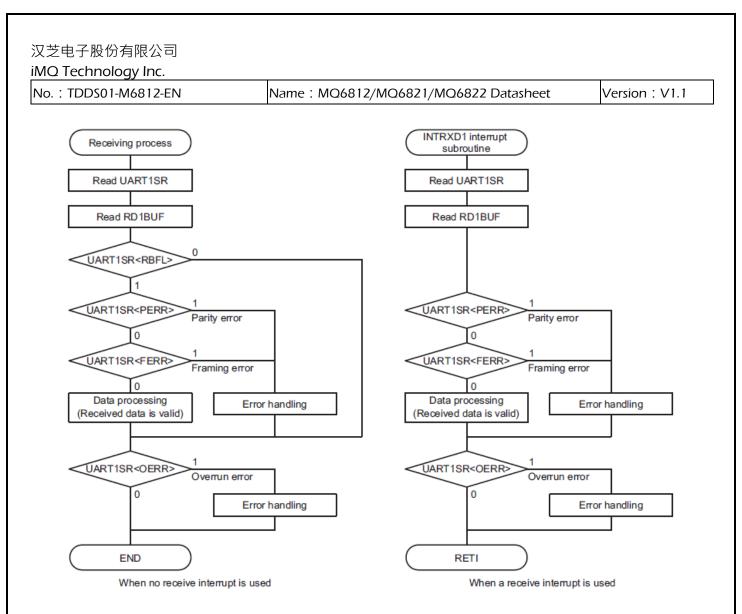

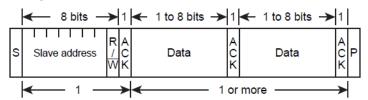

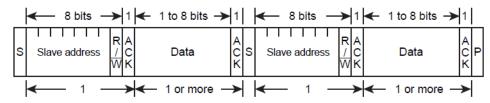

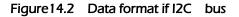

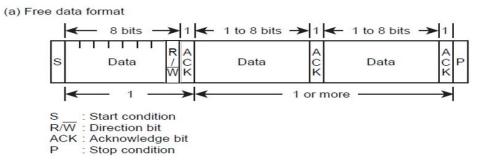

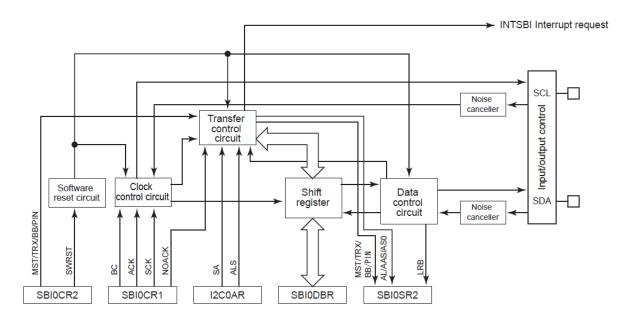

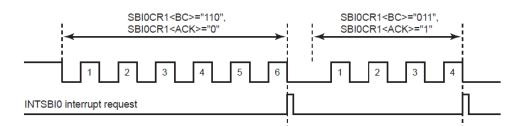

| 14.Serial Bus Interface(SBI)/ I2C                                     | 219 |

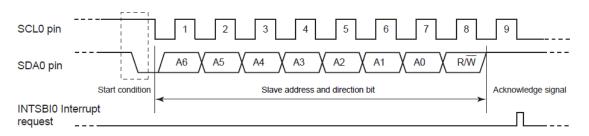

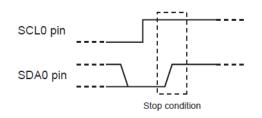

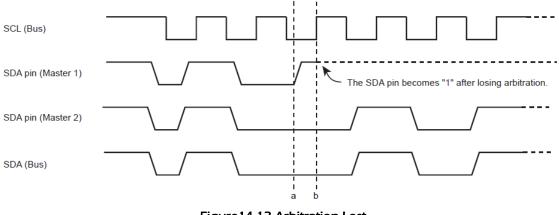

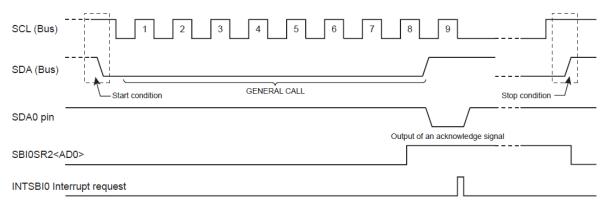

| 14.1 Communication Format                                             | 219 |

| 14.2 Configuration                                                    |     |

| 14.3 Control                                                          | 222 |

| 14.4 Functions                                                        | 227 |

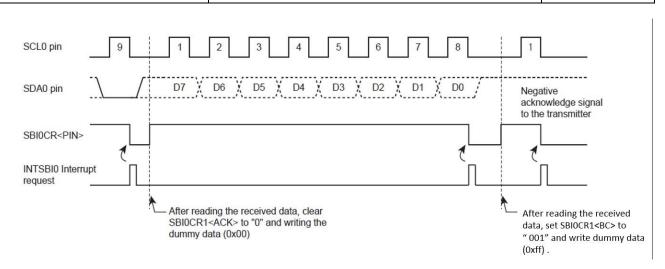

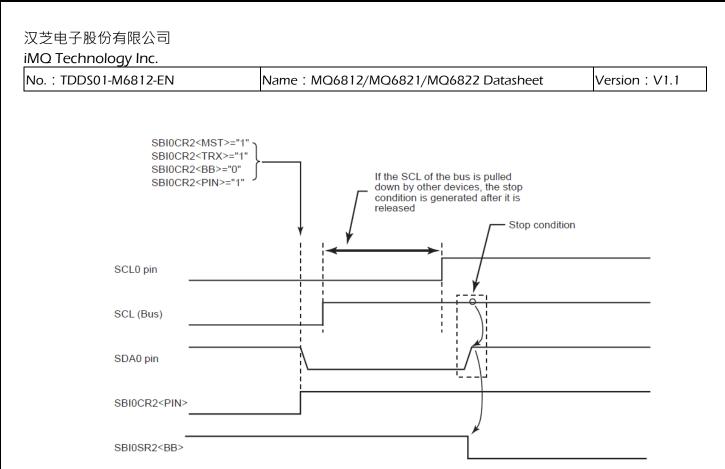

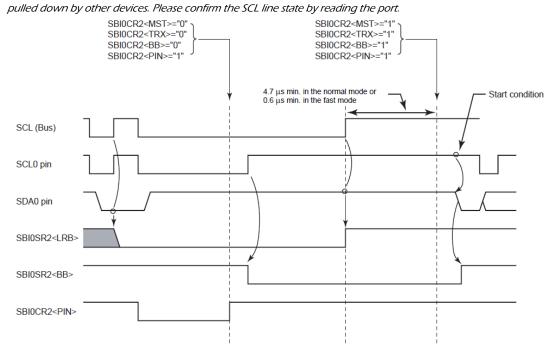

| 14.5 Data transfer of I2C Bus                                         | 239 |

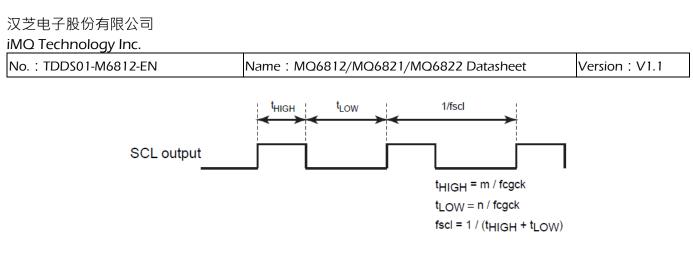

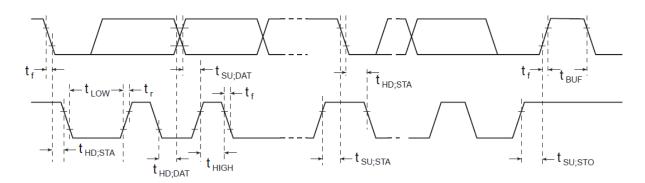

| 14.6 AC Specifications                                                | 246 |

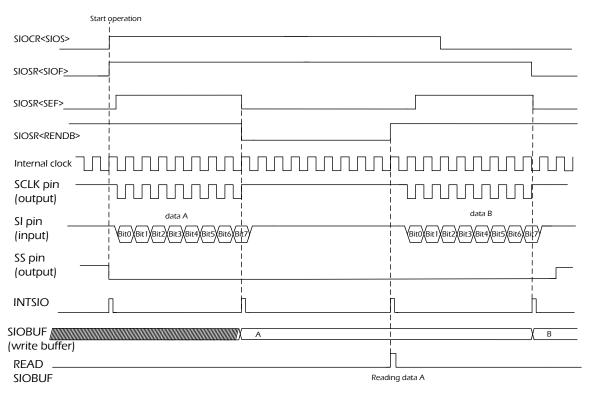

| 15 Synchronous Serial Interface (SIO)                                 | 248 |

| 15.1 Configuration                                                    | 248 |

| 15.2 Control                                                          | 249 |

| 15.3 Low power consumption function                                   | 251 |

| 15.4 Functions                                                        |     |

| 汉芝电子股份有限公司<br>iMQ Technology Inc.                |                                        |                |  |  |  |  |  |  |  |

|--------------------------------------------------|----------------------------------------|----------------|--|--|--|--|--|--|--|

| No. : TDDS01-M6812-EN                            | Name : MQ6812/MQ6821/MQ6822 Datasheet  | Version : V1.1 |  |  |  |  |  |  |  |

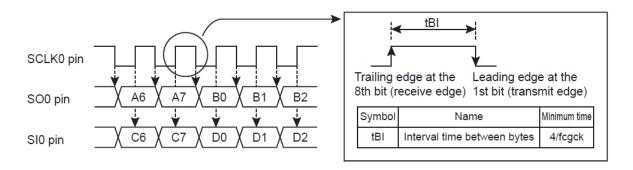

| 15.5 Transfer Modes                              |                                        |                |  |  |  |  |  |  |  |

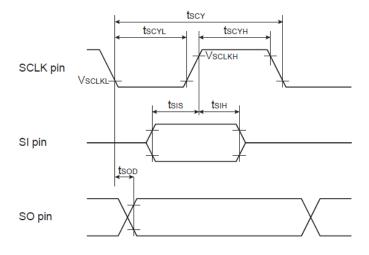

| 15.6 AC Characteristic                           | 15.6 AC Characteristic                 |                |  |  |  |  |  |  |  |

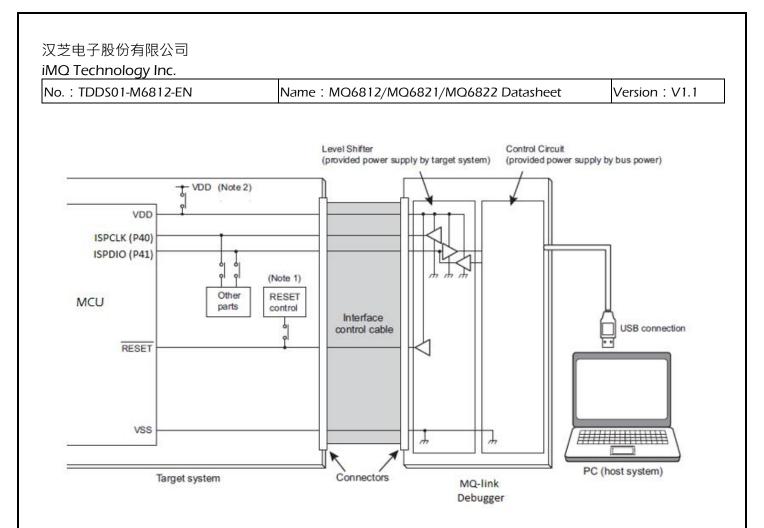

| Appendix A. In-system Programming Function (ISP) |                                        |                |  |  |  |  |  |  |  |

| Appendix B. Product number info                  | Appendix B. Product number information |                |  |  |  |  |  |  |  |

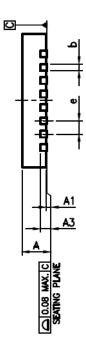

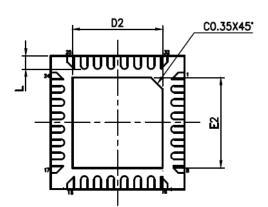

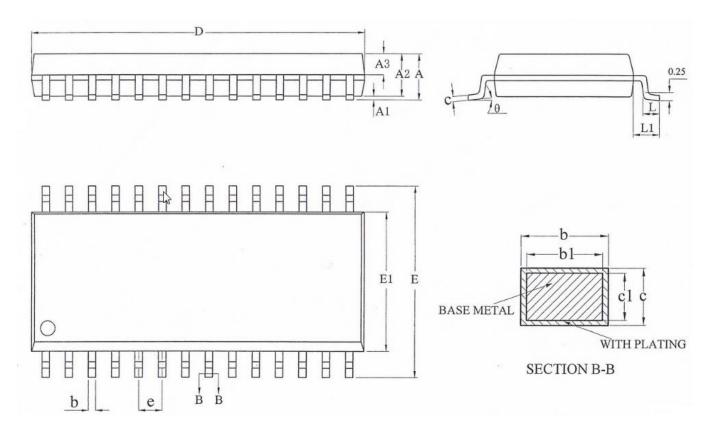

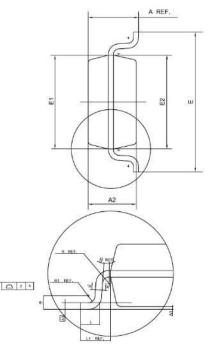

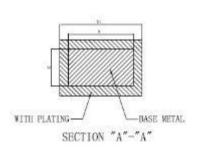

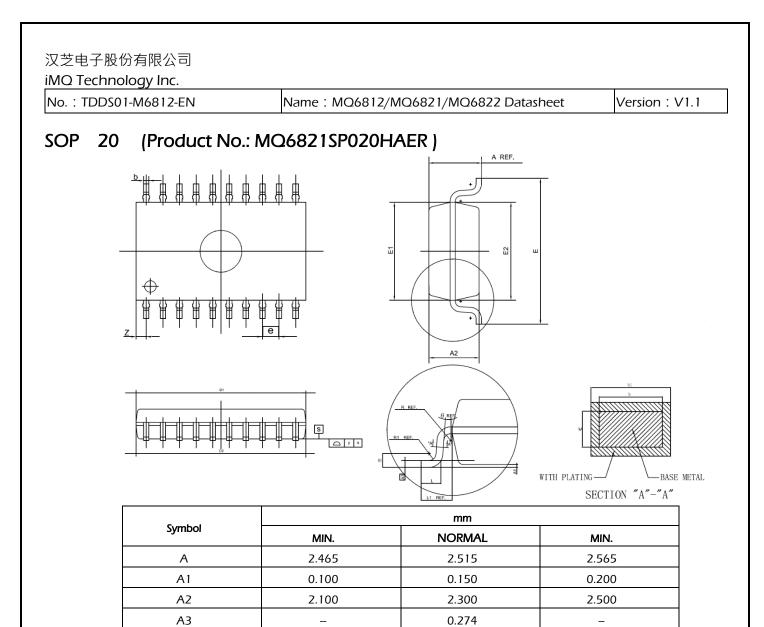

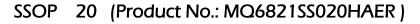

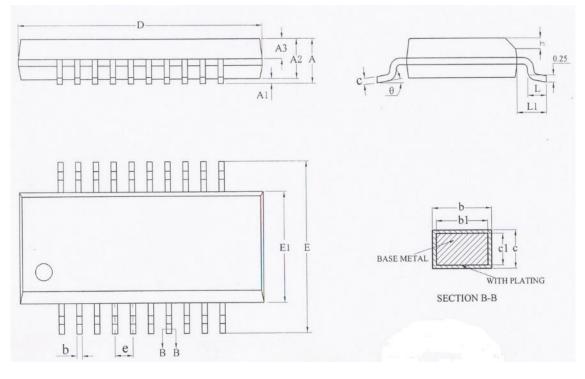

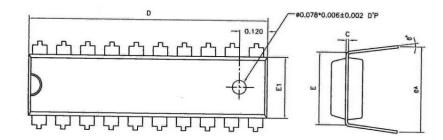

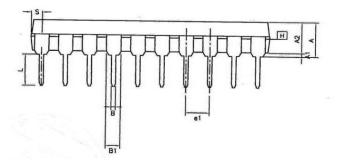

| Appendix C. Package Information                  |                                        |                |  |  |  |  |  |  |  |

| Appendix D. Application Notice                   |                                        |                |  |  |  |  |  |  |  |

Name : MQ6812/MQ6821/MQ6822 Datasheet

## 1. Change History

| Version | Approved Date | Description                                                                                                                                                       |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V 1.0   | 2018/5/3      | New release.                                                                                                                                                      |

| V1.1    | 2021/2/3      | <ol> <li>Update "CH2.3 Pin Assignment", update MQ6822 pin-assignment<br/>and figure 2.2.</li> <li>Update "Appendex C. Package Information" QFN 32(4x4)</li> </ol> |

iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

## 2. Product Overview

## 2.1 Features

- General information

- Wide operating voltage : 2.0V ~ 5.5V

(2.6V ~ 5.5V, when LCD enable)

- Operating temperature: -40°C ~ 85°C

- i87 8-bit MCU core

## Memory

- 16K x 8 program Flash memory (endurance 100K times)

- 512 x 8 data memory RAM

- 64 x 8 information block

## ♦ I/O

- 28 bi-direction I/Os

2 Hi-driving I/O.

- Two 35mA LED driving (P80/P81) other 27 I/O are 15mA output (excluding P10)

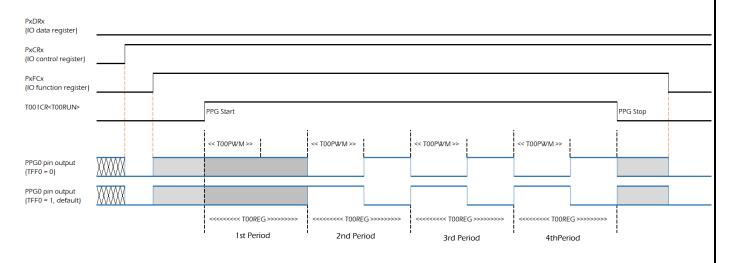

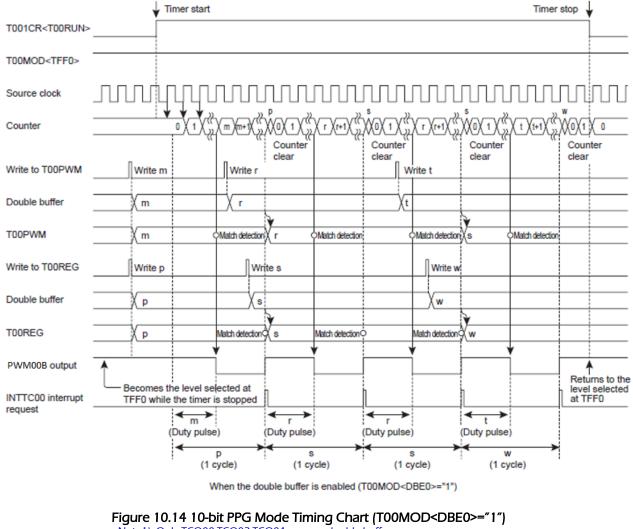

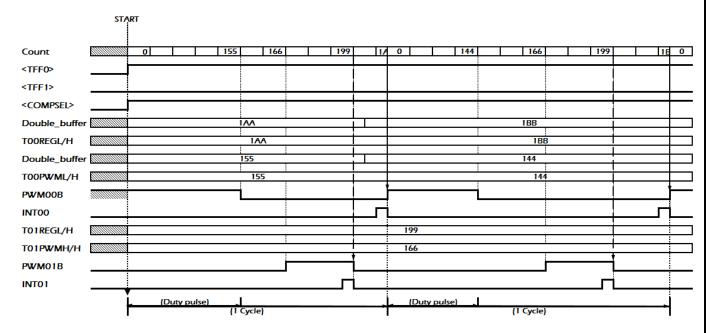

- Max. six 10-bit PPG output

- One16-bit PPG output

- Max. 16 external wake-up pin

- Max. 27 programble pull-up and pulldown I/Os

- 2 UART transfer/receive pins (details description please refer chapter 2.4)

## Instruction cycles

- Instruction cycle can set as 1/1 \ 1/2

1/4 \ 1/8 fc

- 1ch of UART

- 1 sets of SIO

- 1ch of I<sup>2</sup>C/SIO

- 21 interrupt sources

- Max. 18 internal interrupt

- Max 3 external interrupt

## Clock Sources

- External crystal or internal oscillator

- Support 1MHz~16MHz, or 32kHz external crystal

- Internal high oscillator frequency 16MHz

- Internal Low oscillator frequency 24KHz

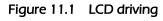

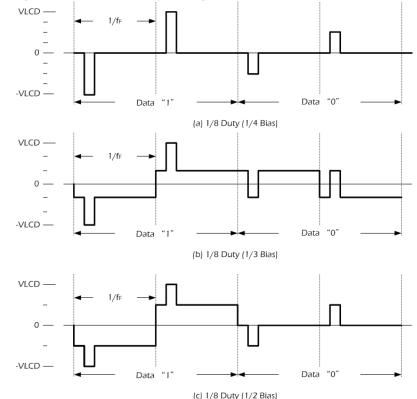

## LCD

- Max. LCD driver up to 8 COM X 12 SEG (DMA)

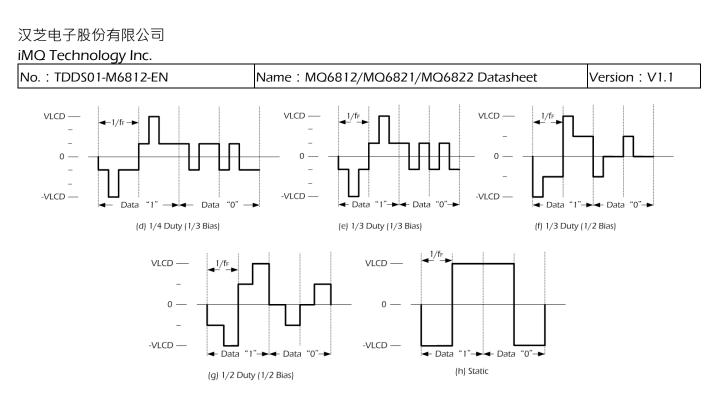

- Eight LCD modes: Static, 1/8 duty(1/4 bias, 1/3 bias, 1/2 bias), 1/4 duty(1/3 bias), 1/3 duty (1/3 bias, 1/2 bias), 1/2 duty(1/2 bias).

## Timer/Counter information

- Max. six 10-bit Timer (TCQ · with capture function)

- TCO00、TCO02、TCO04 with double buffer

- TCQ01、TCQ03、TCQ05 without double buffer

- One 16-bit Timer (TCA · with capture function)

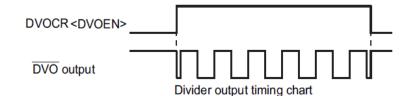

- Time Base Timer(TBT)

- Watch Dog Timer(WDT)

- Watch Dog Timer 2 (WDT2)

- Warm-up Counter (WUC)

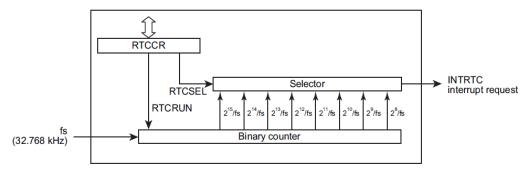

- Real Time Clock (RTC)

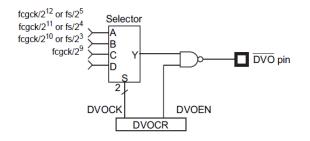

- 8-bit divider output (DVO)

## Low Power Operation Modes

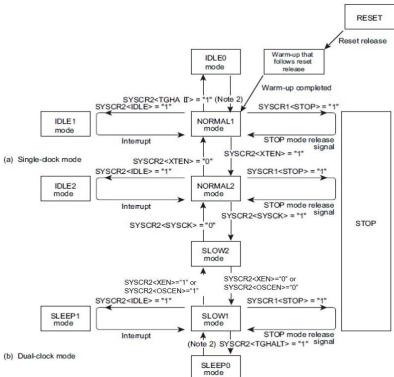

8 low power operation modes: STOP,

SLOW1,SLOW2,IDLE0IDLE1,IDLE2SLEEP0,SLEEP1

## 2set 8-level voltage detect

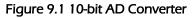

## 10-bit AD converter(ADC)

- Max. 9 external ADC input

- One internal 1/4 VDD battery measure input pin

- Three ADC internal referenc voltage : 4V,3V,2V

- One external ADC referece voltage, voltage range:2.0~5.5V.

## Page: 7/ 278

iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

In-system programming (ISP)

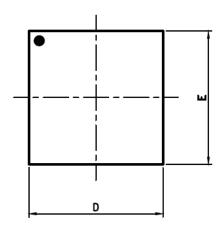

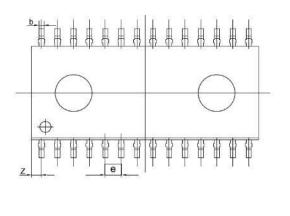

## Package information

- LQFP (7x7)/QFN 32 pin

- SSOP28/SOP28 pin

- SOP/SSOP/DIP20 pin

| Product no.         | MQ6812LQ032HAER                                                 | MQ6812N4032HAER                                                 |  |  |

|---------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Pin cunt./IOs       | 32<br>(30)                                                      | 32<br>(30)                                                      |  |  |

| Operating voltage   | 2.0~5.5V                                                        | 2.0~5.5V                                                        |  |  |

| Operating temp.     | -40~85C                                                         | -40~85C                                                         |  |  |

| Ext. interrupt      | 16                                                              | 16                                                              |  |  |

| Flash               | 16K Bytes                                                       | 16K Bytes                                                       |  |  |

| RAM                 | 512 Bytes                                                       | 512 Bytes                                                       |  |  |

| ADC                 | 10-bit x 9-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> | 10-bit x 9-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> |  |  |

| LCD                 | 8x12                                                            | 8x12                                                            |  |  |

| Interrupt           | External: 3<br>Internal: 18                                     | External: 3<br>Internal: 18                                     |  |  |

| Internal oscillator | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C     | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C     |  |  |

| External crystal    | 1~16MHz or<br>32768Hz                                           | 1~16MHz or<br>32768Hz                                           |  |  |

| Timer/              | 10bit x 6<br>16bit x 1                                          | 10bit x 6<br>16bit x 1                                          |  |  |

| Counter             | WDT,TBT,<br>RTC,WUC                                             | WDT,TBT,<br>RTC,WUC                                             |  |  |

| PWM/PPG             | 10bit x 6<br>16bit x 1                                          | 10bit x 6<br>16bit x 1                                          |  |  |

| LVD                 | 8 level<br>(+/- 0.1V)* <sup>2</sup>                             | 8 level<br>(+/- 0.1V)* <sup>2</sup>                             |  |  |

| Communication       | UART x 1,<br>SIOx1, I <sup>2</sup> Cx1                          | UART x 1,<br>SIOx1, I <sup>2</sup> Cx1                          |  |  |

| ISP                 | Yes                                                             | YEs                                                             |  |  |

| Package type.       | LQFP32                                                          | OFN32                                                           |  |  |

\*1: "1/4 VDD" means there is one internal 1/4 VDD battery measure input pin. "Internal " means there is internal referenc voltage (4V,3V,2V). " External" means there one ne external ADC referece voltage \*2: There is 2 set of LVD, and each set is 4 level voltage, max. accuracy is +/- 0.1V.

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| Product no.            | MQ6812SP028HAER                                                 | MQ6822SP028HAER                                             | MQ6812SS028HAER                                                 |

|------------------------|-----------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|

| Pin cunt./IOs          | 28<br>(26)                                                      | 28<br>(26)                                                  | 28<br>(26)                                                      |

| Operating<br>voltage   | 2.0~5.5V                                                        | 2.0~5.5V                                                    | 2.0~5.5V                                                        |

| Operating temp.        | -40~85C                                                         | -40~85C                                                     | -40~85C                                                         |

| Ext. interrupt         | 13                                                              | 16                                                          | 13                                                              |

| Flash                  | 16K Bytes                                                       | 16K Bytes                                                   | 16K Bytes                                                       |

| RAM                    | 512 Bytes                                                       | 512 Bytes                                                   | 512 Bytes                                                       |

| ADC                    | 10-bit x 9-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> | 10-bit x 9-CH<br>(1/4 VDD, internal,<br>external)*1         | 10-bit x 9-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> |

| LCD                    | 8x8                                                             | 8x12                                                        | 8x8                                                             |

| Interrupt              | External: 2<br>Internal: 19                                     | External: 3<br>Internal: 15                                 | External: 2<br>Internal: 19                                     |

| Internal<br>oscillator | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C     | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C     |

| External crystal       | 1~16MHz or<br>32768Hz                                           | 1~16MHz or<br>32768Hz                                       | 1~16MHz or<br>32768Hz                                           |

| Timer/                 | 10bit x 6<br>16bit x 1                                          | 10bit x 2<br>16bit x 1                                      | 10bit x 6<br>16bit x 1                                          |

| Counter                | WDT,TBT,<br>RTC,WUC                                             | WDT,TBT,<br>RTC,WUC                                         | WDT,TBT,<br>RTC,WUC                                             |

| PWM/PPG                | 10bit x 6<br>16bit x 1                                          | 10bit x 2<br>16bit x 1                                      | 10bit x 6<br>16bit x 1                                          |

| LVD                    | 8 level<br>(+/- 0.1V) <sup>*2</sup>                             | 8 level<br>(+/- 0.1V) <sup>*2</sup>                         | 8 level<br>(+/- 0.1V) <sup>*2</sup>                             |

| Communication          | UART x 1,<br>SIOx1, I <sup>2</sup> Cx1                          | UART x 1,<br>SIOx1, I <sup>2</sup> Cx1                      | UART x 1,<br>SIOx1, I <sup>2</sup> Cx1                          |

| ISP                    | Yes                                                             | Yes                                                         | Yes                                                             |

| Package type.          | SOP28                                                           | SOP28                                                       | SSOP28                                                          |

\*1: "1/4 VDD" means there is one internal 1/4 VDD battery measure input pin. "Internal " means there is internal referenc voltage (4V,3V,2V). " External" means there one ne external ADC referece voltage \*2: There is 2 set of LVD, and each set is 4 level voltage, max. accuracy is +/- 0.1V.

iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version : V1.1

| Product no.         | MQ6821SP020HAER                                                 | MQ6821SS020HAER                                                | MQ6821DP020HAER                                                |

|---------------------|-----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| Pin cunt./IOs       | 20<br>(18)                                                      | 20<br>(18)                                                     | 20<br>(18)                                                     |

| Operating voltage   | 2.0~5.5V                                                        | 2.0~5.5V                                                       | 2.0~5.5V                                                       |

| Operating temp.     | -40~85C                                                         | -40~85C                                                        | -40~85C                                                        |

| Ext. interrupt      | 8                                                               | 8                                                              | 8                                                              |

| Flash               | 16K Bytes                                                       | 16K Bytes                                                      | 16K Bytes                                                      |

| RAM                 | 512 Bytes                                                       | 512 Bytes                                                      | 512 Bytes                                                      |

| ADC                 | 10-bit x 6-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> | 10-bit x6-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> | 10-bit x6-CH<br>(1/4 VDD, internal,<br>external) <sup>*1</sup> |

| Interrupt           | External: 2<br>Internal: 17                                     | External: 2<br>Internal: 17                                    | External: 2<br>Internal: 17                                    |

| Internal oscillator | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C     | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C    | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C    |

| External crystal    | 1~16MHz or 32768Hz                                              | 1~16MHz or<br>32768Hz                                          | 1~16MHz or<br>32768Hz                                          |

| Timer/              | 10bit x 4<br>16bit x 1                                          | 10bit x 4<br>16bit x 1                                         | 10bit x 4<br>16bit x 1                                         |

| Counter             | WDT,TBT,<br>RTC,WUC                                             | WDT,TBT,<br>RTC,WUC                                            | WDT,TBT,<br>RTC,WUC                                            |

| PWM/PPG             | 10bit x 4<br>16bit x 1                                          | 10bit x 4<br>16bit x 1                                         | 10bit x 4<br>16bit x 1                                         |

| LVD                 | 8 level<br>(+/- 0.1V)*2                                         | 8 level<br>(+/- 0.1V) <sup>*2</sup>                            | 8 level<br>(+/- 0.1V)* <sup>2</sup>                            |

| Communication       | UART x 1,SIO x1                                                 | UART x 1, SIOx 1                                               | UART x 1,SIOx1                                                 |

| ISP                 | Yes                                                             | Yes                                                            | Yes                                                            |

| Package type.       | SOP20                                                           | SSOP20                                                         | DIP20                                                          |

\*1: "1/4 VDD" means there is one internal 1/4 VDD battery measure input pin. "Internal " means there is internal referenc voltage (4V,3V,2V). " External" means there one ne external ADC referece voltage

\*2: There is 2 set of LVD, and each set is 4 level voltage, max. accuracy is +/- 0.1V.

iMQ Technology Inc. No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

## 2.2 Block Diagram

## Page: 11/ 278

## Page: 12/ 278

P81 (PPG03B)

P72 (TCA0 / PPGA0B / COMZ)

P73 (<u>KW1</u> 12/COM3)

P83 (PPG05B / COM5)

P82 (PPG04B / COM4)

P23 (SDA / COM6)

P24 (SCL / KWI 8 / COM7

P25 (<u>KW1</u> 9 / SEG0)

汉芝电子股份有限公司 iMQ Technology Inc. No. : TDDS01-M6812-EN Name : MQ6812/MQ6821/MQ6822 Datasheet Version: V1.1 SOP-28/SSOP-28 (LCD: 8COM x 8 SEG) Product No.: MQ6812SP028HAER / MQ6812SS028HAER VSS 0 VDD 28 (XIN) P00 P40 (AIN0 / KWI 0 / OCDCK) 27 (XOUT) P01 P41 (AIN1 / KWL1 / OCDIO) 26 (RESETB) P10 25 P42 (AIN2 / <u>KWI</u> 2) (PPG01B) P71 P43 (AIN3 / <u>KWI</u> 3 / VREF) 24 (COM0 / RX / TX) P90 P44 (AIN4 / <u>KWI</u> 4 / SEG11) 6 23 (COM1 / TX / RX) P91 22 P45 (AIN5 / KWI 5 / SEG10) MQ6812 (PPG02B) P80 21 8 P46 (AIN6 / <u>KWI</u> 6 / SEG9) (PPG03B) P81 20 P47 (AIN7 / <u>KWI</u> 7 / SEG8) 9 (COM2 / PPGA0B / TCA0) P72 10 19 P74 (DVOB / AIN8 / SI / <u>KWI</u> 13 / SEG7) (COM3/<u>KWI</u> 12) P73 11 P76 (INT3 / SCLK / <u>KWI</u> 15 / SEG6) 18 (COM4 / PPG04B) P82 12 P70 (PPG00B / SEG5) 17 (COM5 / PPG05B) P83 P75 (INT2 / SO / KWI 14/ SEG4) 13 16 (COM6 / SDA) P23 15 P24 (SCL / KWI 8 / COM7) 14

Page: 13/ 278

## Page: 14/ 278

Page: 15/ 278

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| 32pin<br>No. | Pin Name                               | LCD<br>(Note 7) | І/О Туре |                                                            | Function Description                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------|-----------------|----------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | vss                                    | -               |          | Power                                                      | Negative power supply/ ground,                                                                                                                                                                                                                                          |

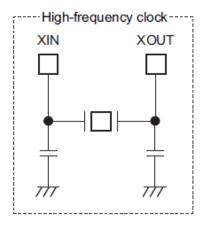

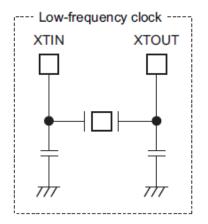

| 2<br>3       | P00/XIN<br>P01/XOUT                    | -               | I/O      | Pull-up<br>Pull-down<br>Ext. crystal<br>(High/Low)         | P00 and P01 are bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>XIN and XOUT are pin-shared with P00 and P01 respectively,<br>and are connected to a high/low frequency external crystal<br>for system clock. |

| 4            | P10/RESETB                             | _               | I/O      | Pull-up(note6)                                             | P10 is bi-directional I/O pins, which are software configurable<br>to be with pull-up resistors.<br>RESETB is pin-shared with P10, which is low-active.                                                                                                                 |

| 5            | P71/ PPG01B                            | _               | I/O      | Pull-up<br>Pull-down                                       | P71 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>8-bit timer/counter pin is pin-shared with P71.                                                                                                        |

| 6<br>7       | P90/TXD1/RXD1<br>P91/RXD1/TXD1         | СОМ0<br>СОМ1    | I/O      | Pull-up<br>Pull-down<br>UART<br>LCD                        | P90, P91 are bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.<br>UART pin TXD0/ RXD0, LCD driving pin COM0/ COM1, are pin-shared with P90, P91 respectively.                                                         |

| 8<br>9       | P80/ PPG02B<br>P81/ PPG03B             |                 | I/O      | Open drain                                                 | P80 and P81 are 35mA current driving output.<br>10-bit timer/counter TCQ02 and TCQ03 are pin-shared with<br>P80, P81 respecttivly.                                                                                                                                      |

| 10           | P72/TCA0/PPGA0B                        | COM2            | I/O      | Pull-up<br>Pull-down<br>LCD                                | P72 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>16-bit timer pin TCA0/ PPGA0B,and LCD driving pin is pin-<br>shared with P72.                                                                          |

| 11           | P73/ <u>KWI</u> 12<br>(note 1, note 6) | СОМЗ            | I/O      | Pull-up<br>Pull-down<br>Wake up<br>LCD                     | P73 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>Wakeup input pin <u>KWI</u> 12 and LCD driving pin COM3 is pin-<br>shared with P73.                                                                    |

| 12<br>13     | P82/PPG04B<br>P83/PPG05B               | COM4<br>COM5    | I/O      | Pull-up<br>Pull-down<br>LCD                                | P82 and P83 are bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>10-bit timer/counter TCO04 < TCO05 ,and LCD driving pin<br>COM4 < COM5 are pin-shared with P82 and P83.                                       |

| 14           | P23/SDA                                | COM6            | I/O      | Pull-up<br>Pull-down<br>I <sup>2</sup> C<br>LCD            | P23 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>I <sup>2</sup> C pin SDA and LCD driving pin COM6 is pin-shared with P23. •                                                                            |

| 15           | P24/SCL./ <u>KWI</u> 8 (note 1)        | COM7            | I/O      | Pull-up<br>Pull-down<br>I <sup>2</sup> C<br>Wake up<br>LCD | P24 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>I <sup>2</sup> C pin SCL and wakeup input pin <u>KWI</u> 8,and LCD driving pin<br>COM7/ SEG31 is pin-shared with P24. °                                |

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| 32pin<br>No.         | Pin Name                                                                          | LCD<br>(Note 7)                |     | І/О Туре                                                        | Function Description                                                                                                                                                                                                                                                                          |

|----------------------|-----------------------------------------------------------------------------------|--------------------------------|-----|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                   | P25/ <u>KWI</u> 9 (note 1)                                                        | SEG0                           | I/O | Pull-up<br>Pull-down<br>Wake up<br>LCD                          | P25 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>Wakeup input pin <u>KWI</u> 9 and LCD driving pin SEG0 is pin-<br>shared with P25.                                                                                           |

| 17<br>18             | P26/ <u>KWI</u> 10<br>P27/ <u>KWI</u> 11<br>(注1)                                  | SEG 1<br>SEG 2                 | I/O | Pull-up<br>Pull-down<br>Wake up<br>LCD                          | P26 and P27 are bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.<br>Wakeup input pin <u>KWI</u> 10, <u>KWI</u> 11 ,and LCD driving pin SEG1, SEG2 are pin-shared with P26, P27 respectiely.                                                |

| 19                   | P77/INT4/SS                                                                       | SEG3                           | I/O | Pull-up<br>Pull-down<br>Ext. interrupt<br>SIO<br>LCD            | P77 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>External interrupt input pin INT4 and (SIO)SS, and LCD driving<br>pin SEG3 is pin-shared with P77.                                                                           |

| 20                   | P75/INT2/ SO/ <u>KWI</u> 14<br>(note 1)                                           | SEG4                           | I/O | Pull-up<br>Pull-down<br>Ext. interrupt<br>SIO<br>Wake up<br>LCD | P75 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>External interrupt input pin INT2, SIO pin SO, wakeup input pin<br><u>KWI</u> 14 and LCD driving SEG4 is pin-shared with P75.                                                |

| 21                   | P70/ PPG00B                                                                       | SEG5                           | I/O | Pull-up<br>Pull-down<br>LCD                                     | <ul> <li>P70 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.</li> <li>8-bit timer/counter pin PPG01B and LCD driving pin SEG5 is pin-shared with P70.</li> </ul>                                                                       |

| 22                   | P76/INT3/SCLK/ <u>KWI</u> 15<br>(注1)                                              | SEG6                           | I/O | Pull-up<br>Pull-down<br>SIO<br>Wake up<br>LCD                   | P76 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>SIO pin SCLK and wakeup input pin <u>KWI</u> 15 and LCD driving<br>pin SEG6 is pin-shared with P76.                                                                          |

| 23                   | P74/DVOB/AIN8/SI/ <u>KWI</u> 13<br>(note1,note 2, note 8)                         | SEG7                           | I/O | Pull-up<br>Pull-down<br>ADC input<br>SIO<br>Wakeup<br>LCD       | P74 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>ADC input pin AIN8 and SIO pin SI, DVO, wakeup input pin <u></u><br><u>KWI</u> 13, and LCD driving pin SEG7 is pin-shared with P74.                                          |

| 24<br>25<br>26<br>27 | P47/AIN7/KWI7<br>P46/AIN6/KWI6<br>P45/AIN5/KWI5<br>P44/AIN4/KWI4<br>(note1,note2) | SEG8<br>SEG9<br>SEG10<br>SEG11 | I/O | Pull-up<br>Pull-down<br>ADC input<br>Wakeup<br>LCD              | P47,P46,P45, and P44 are bi-directional I/O pins, which are<br>software configurable to be with pull-up or pull-down resistors.<br>ADC input AIN7, AIN6,AIN5,AIN4 and wakeup pin <u>KWI 7, KWI</u><br>6, <u>KWI</u> 5, <u>KWI 4</u> are pin-shared with P47, P46,P45 and P44<br>respectively. |

| 28                   | P43/AIN3/ <u>KWI</u> 3/VREF<br>(note1, note2)                                     | -                              | I/O | Pull-up<br>Pull-down<br>ADC input<br>Wakeup                     | P43 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.<br>ADC input pin AIN3 and wakeup pin <u>KWI</u> 3, VREF is pin-shared with P43.                                                                                                    |

iMQ Technology Inc.

No. : TDDS01-M6812-EN

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| 32pin<br>No. | Pin Name                                                                                                | LCD<br>(Note 7) |           | І/О Туре                         | Function Description                                                                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------|-----------------|-----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30           | P42/AIN2/ <u>KWI</u> 2<br>P41/AIN1/ <u>KWI</u> 1/OCDIO<br>P40/AIN0/ <u>KWI</u> 0/OCDCK<br>(note1,note2) | _               | I/O       | Pull-down<br>ADC input<br>Wakeup | P42,P41,and P40 are bi-directional I/O pins, which are<br>software configurable to be with pull-up or pull-down resistors.<br>ADC input AIN2, AIN1,AIN0 and wakeup pin <u>KWI 2 ` KWI</u> 1 `<br><u>KWI</u> 0 are pin-shared with P42, P41 and P40 respectively. |

| 32           | VDD                                                                                                     |                 | Pow<br>er |                                  | Positive power supply                                                                                                                                                                                                                                            |

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| 20pin<br>No. | Pin Name                                 | І/О Туре |                                                                 | Function Description                                                                                                                                                                                                                                                    |

|--------------|------------------------------------------|----------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | VSS                                      | Power    |                                                                 | Negative power supply/ ground,                                                                                                                                                                                                                                          |

| 2<br>3       | P00/XIN<br>P01/XOUT                      | I/O      | Pull-up<br>Pull-down<br>Ext. crystal<br>(High/Low)              | P00 and P01 are bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>XIN and XOUT are pin-shared with P00 and P01 respectively,<br>and are connected to a high/low frequency external crystal<br>for system clock. |

| 4            | P10/RESETB                               | I/O      | Pull-up(note6)                                                  | P10 is bi-directional I/O pins, which are software<br>configurable to be with pull-up resistors.<br>RESETB is pin-shared with P10, which is low-active.                                                                                                                 |

| 5            | P71/TCQ01/PPG01B                         | I/O      | Pull-up<br>Pull-down                                            | P71 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>8-bit timer/counter pin is pin-shared with P71.                                                                                                        |

| 6<br>7       | P90/TXD1/RXD1<br>P91/RXD1/TXD1           | I/O      | Pull-up<br>Pull-down<br>UART<br>LCD                             | P90, P91 are bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>UART pin TXD0/ RXD0, LCD driving pin COM0/ COM1, arepin-<br>shared with P90, P91 respectively.                                                   |

| 8            | P72/TCA0/PPGA0B                          | I/O      | Pull-up<br>Pull-down<br>LCD                                     | P72 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>16-bit timer pin TCA0/ PPGA0B,and LCD driving pin is pin-<br>shared with P72.                                                                          |

| 9<br>10      | P82/PPG04B<br>P83/PPG05B                 | I/O      | Pull-up<br>Pull-down<br>LCD                                     | P82 and P83 are bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>10-bit timer/counter TCQ04 < TCQ05 ,and LCD driving pin<br>COM4 < COM5 are pin-shared with P82 and P83.                                       |

| 11           | P75/INT2/ SO/ <u>KWI</u> 14<br>(note 1)  | I/O      | Pull-up<br>Pull-down<br>Ext. interrupt<br>SIO<br>Wake up<br>LCD | P75 is bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>External interrupt input pin INT2, SIO pin SO, wakeup input pin<br><u>KWI</u> 14 and LCD driving SEG4 is pin-shared with P75.                          |

| 12           | P70/ PPG00B                              | I/O      | Pull-up<br>Pull-down<br>LCD                                     | P70 is bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>8-bit timer/counter pin PPG01B and LCD driving pin SEG5 is<br>pin-shared with P70.                                                                     |

| 13           | P76/INT3/SCLK/ <u>KWI</u> 15<br>(note 1) | I/O      | Pull-up<br>Pull-down<br>SIO<br>Wake up<br>LCD                   | P76 is bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>SIO pin SCLK and wakeup input pin <u>KWI</u> 15 and LCD driving<br>pin SEG6 is pin-shared with P76.                                                    |

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

| 20pin<br>No.   | Pin Name                                                                                                | І/О Туре |                                                     | Function Description                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | P74/DVOB/AIN8/SI/ <u>KWI</u> 13<br>(note1,note 2, note 8)                                               | I/O      | Pull-up<br>Pull-down<br>ADC input<br>SIO<br>Wakeup  | P74 is bi-directional I/O pins, which are software configurable<br>to be with pull-up or pull-down resistors.<br>ADC input pin AIN8 and SIO pin SI, DVO, wakeup input pin_<br><u>KWI</u> 13, and LCD driving pin SEG7 is pin-shared with P74.                    |

| 15             | P44/AIN4/ <u>KWI</u> 4<br>(note1,note2)                                                                 | I/O      | Pull-up<br>Pull-down<br>ADC input<br>Wakeup         | P44 is bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>ADC input pin AIN4 and wakeup pin <u>KWI</u> 4 is pin-shared with<br>P43.                                                                       |

| 16             | P43/AIN3/ <u>KWI</u> 3/VREF<br>(note1, note2)                                                           | I/O      | Pull-up<br>Pull-down<br>ADC input<br>Wakeup         | P43 is bi-directional I/O pins, which are software<br>configurable to be with pull-up or pull-down resistors.<br>ADC input pin AIN3 and wakeup pin <u>KWI</u> 3, VREF is pin-<br>shared with P43.                                                                |

| 17<br>18<br>19 | P42/AIN2/ <u>KWI</u> 2<br>P41/AIN1/ <u>KWI</u> 1/OCDIO<br>P40/AIN0/ <u>KWI</u> 0/OCDCK<br>(note1,note2) | I/O      | Pull-up<br>Pull-down<br>ADC input<br>Wakeup<br>OCDE | P42,P41,and P40 are bi-directional I/O pins, which are<br>software configurable to be with pull-up or pull-down resistors.<br>ADC input AIN2, AIN1,AIN0 and wakeup pin <u>KWI 2 × KWI</u> 1 ×<br><u>KWI</u> 0 are pin-shared with P42, P41 and P40 respectively. |

| 20             | VDD                                                                                                     | Power    |                                                     | Positive power supply                                                                                                                                                                                                                                            |

Note 1 : <u>KWI</u> 0~<u>KWI</u> 15 can define to system wake up input pin. <u>KWI</u> 0~<u>KWIZ</u> are pin-shared with P40~P47, and <u>KWI</u> 8~<u>KWI</u> 15 are pin-shared with P24~P27, 73~P76 respectively.

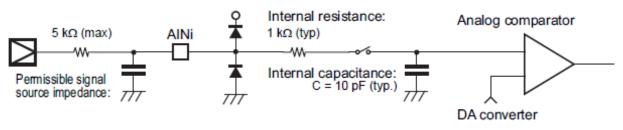

Note 2 : AIN0~AIN8 and AIN13~AIN15 are10-bit ADC input pins.

Note 3: OCD pin are VSS, VDD, P10, P40 and P41. Please note, under OCDE mode, P10,P40 and P40 can not execute the pin function.

Note4: LCD enablem please set LCD driving pin/COM and SEG) as input mode. And keep LCD operating voltage same with VDD of MCU.

Note5 : If using P74 as ADC input/AIN8), and also enable other ADC input pin/AIN), it will cost extra power in stop mode. Please avoid P74 as AIN function/AIN8) if possible.

Note6: The I/O pins which need to be pull-high or pull-low should be connected to VDD or GND through a resistor (resistance >100ohm). To connect I/O pins to VDD or GND directly should be avoided.

## Page: 20/ 278

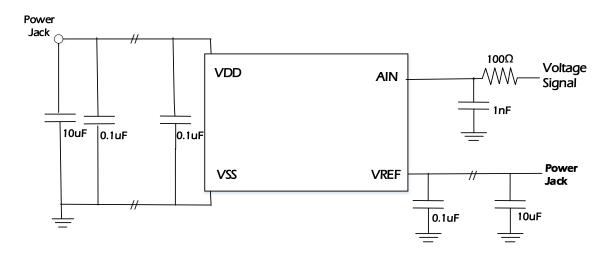

Figure 2.2 is MQ6812/MQ6822/MQ6821 suggestion external reference circuit · as below 3 parts:

- 1. Add 10uF and 0.1uF capacitance parallel connection to VDD and VSS. In order to avoid power surge or noise effect, it can also enhance MCU EFTB performance. The capacitance position should be close to VDD and VSS pin as close as possible.

- 2. Use ADC function, please series a 100ohm and 1nF capacitance to groud. This can filter noise.

- 3. Connecting 0.1uF capacitor where is near IC, and add (10uF +0.1 uF) capacitor closed to the power jack are recommended. Use ADC and ADC external reference voltage, please add 10uF and 0.1uF capacitance parallel connection, this can filter noise.

Figure 2.2 recommended external circuit

Name : MQ6812/MQ6821/MQ6822 Datasheet

## 3. Electronic Characteristics

## 3.1 Absolute Maximum Ratings

The absolute maximum ratings are rated value which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

|                        |                   |                                   | (\                            | $V_{SS} = 0V$ |  |

|------------------------|-------------------|-----------------------------------|-------------------------------|---------------|--|

| Parameter              | Symbol            | Pins                              | Max.                          | Unit          |  |

| Operating voltage      | V <sub>DD</sub>   |                                   | -0.3 to 6.0                   | V             |  |

| Input voltage          | V <sub>IN</sub>   | All I/O pins                      | -0.3 to $V_{\text{DD}}$ + 0.3 | V             |  |

| Output voltage         | V <sub>OUT</sub>  | All I/O pins                      | -0.3 to $V_{\text{DD}}$ + 0.3 | V             |  |

|                        | I <sub>OUT1</sub> | P10 (IOL)                         | 15                            |               |  |

| Output current         | I <sub>OUT2</sub> | All I/O pins ,excluding P10 (IOL) | 40                            | mA            |  |

| (per-pin)              | I <sub>OUT3</sub> | All I/O pins (IOH)                | -15                           |               |  |

|                        | I <sub>OUT4</sub> | P80/P81 LED driving port)         | 60                            |               |  |

|                        | $\Sigma I_{OUT1}$ | All I/O pins (IOL)                | 120                           | mΛ            |  |

| Output current (total) | $\Sigma I_{OUT2}$ | All I/O pins (IOH)                | 60                            | mA            |  |

| Storage temperature    | T <sub>STG</sub>  |                                   | -40 to 125                    | °C            |  |

| Operating temperature  | T <sub>OPR</sub>  |                                   | -40 to 85                     | °C            |  |

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

## Page: 22/ 278

### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

## 3.2 Operation Conditions

|            |                              |                   |                                              |                                            | $(V_{SS} = $  | OV, T <sub>OPR</sub> = | -40 to 85             | °C)  |

|------------|------------------------------|-------------------|----------------------------------------------|--------------------------------------------|---------------|------------------------|-----------------------|------|

| Parame     | eter                         | Symb<br>ol        | Pins                                         | Condition                                  | Min           | Тур.                   | Max                   | Unit |

| Supply vo  | ltage                        | V <sub>DD</sub>   | LCD disable                                  |                                            | 2.0           | -                      | 5.5                   | V    |

| Supply Vo  | lage                         | v DD              | LCD enable                                   | 所有工作模式                                     | 2.6           | -                      | 5.5                   | V    |

| Input high | n level                      | VIH               | All I/O pins                                 | MALIFIKA                                   | $V_{DD}x0.75$ | -                      | V <sub>DD</sub>       | V    |

| Input low  | level                        | VIL               | All I/O pins                                 |                                            | 0             | -                      | V <sub>DD</sub> x0.25 | V    |

|            | Ext.<br>crystal<br>(high)    | f <sub>C</sub>    | XIN, XOUT                                    |                                            |               | -                      | 16                    | MHz  |

|            | Ext.<br>crystal<br>(low)     | f <sub>CL</sub>   | XIN, XOUT (32.768KHz)                        | V <sub>DD</sub> = 2.0 to 5.5V              | 30.0          | 32.768                 | 34.0                  | KHz  |

| Clock      |                              |                   |                                              | V <sub>DD</sub> = 2.0 to 5.5V<br>25°C      | -1%           |                        | +1%                   | MHz  |

| Frequency  | Internal<br>crystal          |                   | FSCTRL <fosccks>="01" - 16MHz</fosccks>      | V <sub>DD</sub> = 2.0 to 5.5V<br>0°C ~85°C | -2%           | 16.00                  | +2%                   | MHz  |

| (high)     |                              |                   | V <sub>DD</sub> = 2.0 to 5.5V<br>-40°C ~85°C | -3%                                        |               | +3%                    | MHz                   |      |

|            | Internal<br>crystal<br>(low) | f <sub>OSCL</sub> | 24KHz                                        | V <sub>DD</sub> = 2.0 to 5.5V              | -             | 24                     | -                     | KHz  |

|            | System<br>clock              | f <sub>ссск</sub> | Set CGCR <fcgcksel></fcgcksel>               | V <sub>DD</sub> = 2.0 to 5.5V              | 0.125         | -                      | 16                    | MHz  |

## 3.3 DC Characteristics

|                       |                  |                                                          |                                                   | (V <sub>SS</sub> = | • OV, T <sub>OPR</sub> | = -40 to | 85°C) |

|-----------------------|------------------|----------------------------------------------------------|---------------------------------------------------|--------------------|------------------------|----------|-------|

| Parameter             | Symbol           | Pins                                                     | Condition                                         | Min                | Тур.                   | Max      | Unit  |

| Hysteresis<br>voltage | V <sub>HS</sub>  | All I/O pins                                             |                                                   | -                  | 0.9                    | -        | V     |

| Input current         | I <sub>IN</sub>  | All I/O pins                                             | $V_{DD} = 5.5V$                                   | -                  |                        | ±2       | μA    |

| Pull-up<br>resistance | R <sub>UP</sub>  | All I/O pins · excluding<br>P80/P81 · P10 RESETB disalbe | V <sub>IN</sub> = 5.5V / 0V                       | 30                 | 50                     | 70       | ΚΩ    |

| Pull-down             |                  | All I/O pins ` excluding                                 | $V_{DD}/V_{IN} = 5.5V$                            | 27.5               | 55                     | 88       | ΚΩ    |

| resistance            | R <sub>DN</sub>  | P10/P80/P81                                              | $V_{DD}/V_{IN} = 2.0V$                            | -                  | 200                    | -        | KΩ    |

|                       | I <sub>OL1</sub> | P10                                                      |                                                   | 3.0                | 5.0                    |          | mA    |

| Output                | I <sub>OL2</sub> | All I/O pins · excluding<br>P10/P80/P81                  | V <sub>DD</sub> = 5.5V<br>V <sub>OL</sub> = 0.55V | 9.0                | 15.0                   | -        | mA    |

| leakage               | I <sub>OL3</sub> | P80/P81                                                  |                                                   | 21.0               | 35.0                   | -        | mA    |

| current               | I <sub>OH1</sub> | All I/O pins · excluding<br>P80/P81                      | $V_{DD} = 5.5V$                                   | 3.0                | 5.0                    | _        | mA    |

|                       | I <sub>OH2</sub> | P80/P81                                                  | V <sub>OH</sub> = 4.95V                           | 9.0                | 15.0                   | -        | mA    |

Note2 : Data in "Typ." column is at  $T_{OPR} = 25^{\circ}C$ ,  $V_{DD} = 5.0V$ , unless otherwise stated.

iMQ Technology Inc.

No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

|                                           |                   |                                                                      | $(V_{SS} = 0V, T_{OPR} = 25^{\circ}C)$ |      |     | °C)  |

|-------------------------------------------|-------------------|----------------------------------------------------------------------|----------------------------------------|------|-----|------|

| Parameter                                 | Symbol            | Condition                                                            | Min                                    | Тур. | Max | Unit |

| Operating current in<br>NORMAL 1, 2 modes |                   | $V_{DD} = 5.5V$                                                      |                                        | 3.8  | 4.4 |      |

| Operating current in IDLE0, 1, 2 modes    |                   | $f_{cgck} = \frac{16.0 \text{ MHz}}{f_{S}}$ $f_{S} = 24 \text{ KHz}$ |                                        | 2.2  | 2.6 |      |

| Operating current in NORMAL 1, 2 modes    |                   | $V_{DD} = 5.5V$                                                      |                                        | 3.1  | 3.7 | mA   |

| Operating current in IDLE0, 1, 2 modes    |                   | f <sub>cgck</sub> = <u>8.0 MHz</u><br>f <sub>S</sub> = 24 KHz        |                                        | 2.0  | 2.4 |      |

| Operating current in<br>SLOW1 modes       | - I <sub>DD</sub> |                                                                      |                                        | 32   | 45  |      |

| Operating current in<br>SLEEP1 modes      |                   | $V_{DD} = 3.0V$<br>$f_s = 24$ KHz                                    |                                        | 19   | 28  |      |

| Operating current in<br>SLEEP0 modes      |                   |                                                                      |                                        | 19   | 28  | μΑ   |

| Operating current in<br>STOP modes        |                   | V <sub>DD</sub> = 5.5V                                               | _                                      | 8    | 12  |      |

Note1 : Data in "Typ." column is at Torr = 25°C, VDD = 5.0V, unless otherwise stated.

Note2 : Each supply current in SLOW2 mode is equivalent to that in IDLE0, IDLE1 and IDLE2 modes.

|                                           | $(V_{SS} = 0V, T_{OPR} = -40 \text{ to } 85)$ |                                                                      |     |      |     | 85°C) |

|-------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------|-----|------|-----|-------|

| Parameter                                 | Symbol                                        | Condition                                                            | Min | Тур. | Max | Unit  |

| Operating current in<br>NORMAL 1, 2 modes |                                               | $V_{DD} = 5.5V$                                                      | -   | 3.8  | 4.8 |       |

| Operating current in IDLE0, 1, 2 modes    |                                               | $f_{cgck} = \frac{16.0 \text{ MHz}}{f_{S}}$ $f_{S} = 24 \text{ KHz}$ |     | 2.2  | 3.0 |       |

| Operating current in<br>NORMAL 1, 2 modes |                                               | $V_{DD} = 5.5V$                                                      | -   | 3.1  | 4.1 | mA    |

| Operating current in IDLE0, 1, 2 modes    |                                               | $f_{cgck} = \frac{8.0 \text{ MHz}}{f_S}$<br>$f_S = 24 \text{ KHz}$   |     | 2.0  | 2.8 |       |

| Operating current in<br>SLOW1 modes       | - I <sub>DD</sub>                             |                                                                      | -   | 32   | 148 |       |

| Operating current in<br>SLEEP1 modes      |                                               | $V_{DD} = 3.0V$<br>$f_s = 24 \text{ KHz}$                            |     | 19   | 129 |       |

| Operating current in<br>SLEEP0 modes      |                                               |                                                                      |     | 19   | 128 | μA    |

| Operating current in<br>STOP modes        |                                               | V <sub>DD</sub> = 5.5V                                               |     | 8    | 92  |       |

Note1 : Data in "Typ." column is at Topr = 25°C, VDD = 5.0V, unless otherwise stated.

Note2 : Each supply current in SLOW2 mode is equivalent to that in IDLE0, IDLE1 and IDLE2 modes.

Name : MQ6812/MQ6821/MQ6822 Datasheet

~ /

$\alpha (\gamma \gamma \gamma) (\gamma \gamma \gamma)$

Version: V1.1

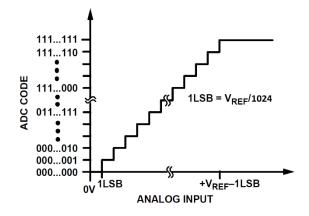

## 3.4 AD Conversion Characteristics

|                                          |                  | $(V_{SS} = 0V, 2.7V)$                      | $ \geq V_{DD} $ | $\geq$ 5.5V, | $I_{OPR} = Z_{2}^{2}$ | S () |

|------------------------------------------|------------------|--------------------------------------------|-----------------|--------------|-----------------------|------|

| Parameter                                | Symbol           | Condition                                  | Min             | Тур.         | Max                   | Unit |

| Analog Reference Voltage                 | V <sub>REF</sub> | -                                          |                 |              | V <sub>DD</sub>       | V    |

| Analog input voltage range               | VAIN             | -                                          | V <sub>SS</sub> |              | $V_{DD}$              | V    |

| Conversion Time                          |                  | fcgck = 2MHz<br>ADCCR2 <ack> = "000"</ack> | -               | 16.0         | -                     | μs   |

| Differential Nonlinearity Error<br>(DNL) |                  | -                                          | -               |              | ±2.0                  | LSB  |

| Integral Nonlinearity Error<br>(INL)     |                  | -                                          | -               |              | ±2.0                  | LSB  |

| Zero Point Error                         |                  | -                                          |                 |              | ±2.0                  | LSB  |

| Full Scale Error                         |                  | -                                          |                 |              | ±2.0                  | LSB  |

| Total Error                              |                  | -                                          |                 |              | ±2.0                  | LSB  |

< F F) / T

| Barameter                                | Sumbol           | Condition                                  | Min | Tre  | Max             | Unit |

|------------------------------------------|------------------|--------------------------------------------|-----|------|-----------------|------|

| Parameter                                | Symbol           | Condition                                  | Min | Тур. | Max             | Unit |

| Analog Reference Voltage                 | V <sub>REF</sub> | -                                          |     |      | $V_{DD}$        | V    |

| Analog input voltage range               | V <sub>AIN</sub> | -                                          | Vss | -    | V <sub>DD</sub> | V    |

| Conversion Time                          |                  | fcgck = 2MHz<br>ADCCR2 <ack> = "001"</ack> | _   | 32.0 |                 | μs   |

| Differential Nonlinearity Error<br>(DNL) |                  | -                                          | -   | -    | ±4.0            | LSB  |

| Integral Nonlinearity Error<br>(INL)     |                  | -                                          | _   | _    | ±4.0            | LSB  |

| Zero Point Error                         |                  | -                                          | -   | -    | ±4.0            | LSB  |

| Full Scale Error                         |                  | -                                          | -   | -    | ±4.0            | LSB  |

| Total Error                              |                  | -                                          |     |      | ±4.0            | LSB  |

Note1: The total error includes all errors except a quantization error, and is defined as the maximum deviation from the ideal conversion line.

Note 2 : The voltage to be input to the AIN input pin must be within the range  $V_{REF}$  to  $V_{SS}$ . If a voltage outside this range is input, converted values will become indeterminate, and converted values of other channels will be affected.

Name : MQ6812/MQ6821/MQ6822 Datasheet

Version: V1.1

## 3.5 Flash Characteristics

|                                               | $(V_{SS} = 0V, 2)$                     | $2.0V \leq V_{I}$ | $_{\rm DD} \leq 5.5 V_{\rm c}$ | , T <sub>OPR</sub> = -40 | to 85°C) |

|-----------------------------------------------|----------------------------------------|-------------------|--------------------------------|--------------------------|----------|

| Parameter                                     | Condition                              | Min               | Тур.                           | Max                      | Unit     |

| Number of guaranteed write to<br>flash memory |                                        | -                 |                                | 100,000                  | times    |

| Flash memory write time                       |                                        |                   |                                | 40                       | μs       |

|                                               | chip erase                             | -                 | -                              | 40                       |          |

| Flash memory erase time                       | sector erase<br>(1 sector = 128 Bytes) | -                 | -                              | 5                        | ms       |

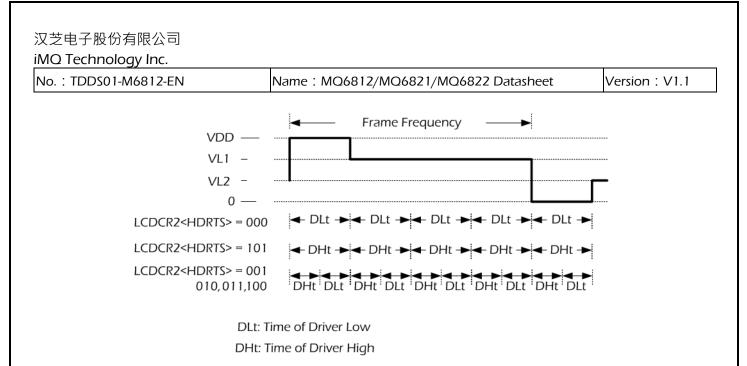

## 3.6 LCD Characteristics

|                       |                 |                                       |      | (V <sub>SS</sub> = | = 0V, T <sub>OPR</sub> = | = 25°C) |

|-----------------------|-----------------|---------------------------------------|------|--------------------|--------------------------|---------|

| Parameter             | Symbol          | Condition                             | Min  | Тур.               | Max                      | Unit    |

| LCD operating volateg | V <sub>DD</sub> |                                       | 2.6  | -                  | 5.5                      | V       |

|                       |                 | 1/4 bias LCD, V <sub>DD</sub> = 5.0V  | 3.19 | 3.75               | 4.31                     | V       |

| LCD bias output 1     | V <sub>L1</sub> | 1/3 bias LCD, V <sub>DD</sub> = 5.0V  | 2.83 | 3.33               | 3.83                     | V       |

|                       |                 | 1/2 bias LCD, V <sub>DD</sub> = 5.0V  | 2.12 | 2.50               | 2.88                     | V       |

|                       | V <sub>L2</sub> | 1/42 bias LCD, V <sub>DD</sub> = 5.0V | 2.12 | 2.50               | 2.88                     | V       |

| LCD bias output 2     |                 | 1/32 bias LCD, V <sub>DD</sub> = 5.0V | 1.42 | 1.67               | 1.92                     | V       |

| LCD bias output 3     | V <sub>L3</sub> | 1/4 bias LCD, V <sub>DD</sub> = 5.0V  | 1.06 | 1.25               | 1.44                     | V       |

Name : MQ6812/MQ6821/MQ6822 Datasheet

## 4. Central Processing Unit (CPU)

## 4.1 General Concept

MQ6812/MQ6821 adopts i87 8-bit MCU core with embedded 16KB program flash memory, and 128 x8 bit data flash. The introduction of the powerful central processing unit (CPU) can be divided into two major parts: (1) Addressing Space of Program / Data Memory and Special Function Registers (SFR), (2) Operation Modes.

## 4.2 Addressing Space

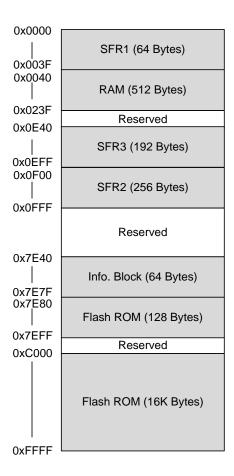

Figure 4.1 shows the addressing space of MQ6812/MQ6821, including SRF1, SRF2, SFR3, RAM and program memory (Flash) memory. Except main 16KB program flash memory, and 128 x8 bit data flash, MQ6812/MQ6821 also provide 64x8 bit info. block(0x7E40  $\cong$  0x7E7F).Info block can save important product information, e.g. information of writer.

Figure 4.1 Addressing Map of MQ6812/MQ6821

Page: 27 / 278

## 4.2.1 Program Memory- Flash

The program memory (Flash) is used to store the program instructions which are to be executed. It also contains data, table, and interrupt entries, and is organized into 16K + 128 bytes format which is addressed by the PC and table pointer. The Flash ranges of MQ6812/MQ6821 is from 0xC000 to 0xFFFF (16K bytes) The data flash ranges of MQ6812/MQ6821 is from 0x7E80 to 0x7EFF (128x8) .The 128 x 8 byte area can use for saving user information, e.g. product ID.  $\circ$

## 4.2.2 RAM Data Memory- RAM

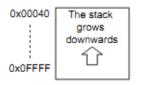

The RAM is mapped to 0x0040 to 0x023F(512x 8 byte) in the data area after reset release. Note that the contents of the RAM become unstable when the power is turned on and immediately after a reset is released. To execute the program by using the RAM, transfer the program to be executed in the initialization routine.

## 4.2.3 Special Function Register-SFR

The SFR is mapped to 0x0000 to 0x003F (SFR1), 0x0F00 to 0x0FFF (SFR2) and 0x0E40 to 0x0EFF (SFR3) in the data area after reset release.

note: do not read SFR which is system reserved.

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

## Page: 28/ 278

## iMQ Technology Inc. No. : TDDS01-M6812-EN

#### Name : MQ6812/MQ6821/MQ6822 Datasheet

|        | SER 1                     |

|--------|---------------------------|

|        |                           |

| 0x0000 | PODR                      |

| 0x0001 | P1DR                      |

| 0x0002 | PZDR                      |

| 0x0003 | 1201                      |

|        | P4DR                      |

| 0x0004 | P4DK                      |

| 0x0005 |                           |

| 0x0006 |                           |

| 0x0007 | P7DR                      |

| 0x0008 | P8DR                      |

| 0x0009 | P9DR                      |

| 0x000A | 170%                      |

|        |                           |

| 0x000B |                           |

| 0x000C |                           |

| 0x000D | POPRD                     |

| 0x000E | P1PRD                     |

| 0x000F | P2PRD                     |

| 0x0010 | 12110                     |

| 0x0011 | P4PRD                     |

|        | P4PKD                     |

| 0x0012 |                           |

| 0x0013 |                           |

| 0x0014 | P7PRD                     |

| 0x0015 | P8PRD                     |

| 0x0016 | P9PRD                     |

| 0x0017 | 17/10                     |

|        |                           |

| 0x001E |                           |

| 0x001E | SIOOCR                    |

|        |                           |

| 0x0020 | SIOOSR                    |

| 0x0021 | SIOOBUF                   |

| 0x0022 | SBIOCR1                   |

| 0x0023 | SBIOCR2/SBIOSR2<br>I2COAR |

| 0x0024 | 12COAR                    |

| 0x0025 | SBIODBR                   |

| 0x0026 | 3010001                   |

| 0x0020 |                           |

| 0x0029 |                           |

| 0x002A | T00MOD                    |

| 0x002B | T01MOD                    |

|        | TOTMOD                    |

| 0x002C | T001CR                    |

| 0x002D | TAODRAL                   |

| 0x002E | TAODRAH                   |

| 0x002F | TAODRBL                   |

| 0x0030 | TAODRBH                   |

| 0x0031 | TAOMOD                    |

|        | TAOR                      |

| 0x0032 |                           |

| 0x0033 | TAOSR                     |

| 0x0034 | ADCCR1                    |

| 0x0035 | ADCCR2                    |

| 0x0036 | ADCCRL                    |

| 0x0037 | ADCCRH                    |

| 0x0037 | DVOCR                     |

|        |                           |

| 0x0039 | TBTCR                     |

| 0x003A | EIRL                      |

| 0x003B | EIRH                      |

| 0x003C | EIRE                      |

| 0x003D | EIRD                      |

| 0x003E | LIND                      |

| 0x003F | PSW                       |

| 000031 | FSW                       |

| SFR2                                       |

|--------------------------------------------|

| POPD                                       |

| 0300                                       |

| PZPD                                       |

| P4PD                                       |

| 1110                                       |

|                                            |

| P7PD<br>P8PD                               |

| P8PD                                       |

| P9PD                                       |

|                                            |

|                                            |

| POCR<br>P1CR<br>P2CR                       |

| PICR                                       |

| P2CR                                       |

| DACD                                       |

| P4CR                                       |

|                                            |

| P7CR<br>P8CR                               |

| P8CR                                       |

| P9CR                                       |

|                                            |

|                                            |

| POPU                                       |

| PIPU                                       |

| P2PU                                       |

|                                            |

| 07011                                      |

| P7PU<br>P8PU                               |

| P8PU<br>P9PU                               |

| 1910                                       |

|                                            |

|                                            |

| POFC                                       |

| 0350                                       |

| P2FC                                       |

| P4FC                                       |

| LALC .                                     |

|                                            |

| P7FC                                       |

| P8FC                                       |

| P9FC                                       |

|                                            |

| P2OUTCR                                    |

| 1200101                                    |

|                                            |

| UARTICRI<br>UARTICR2<br>UARTIDR<br>UARTISR |

| UART1CR2                                   |

| UARTIDR                                    |

| UARTISR<br>TD1BUF / RD1BUF                 |

| TO BOF / KD BOF                            |

|                                            |

|                                            |

| POFFCR0<br>POFFCR1<br>POFFCR2              |

| POFFCR1                                    |

| POFFCR2<br>POFFCR3                         |

| POFFCR3                                    |

|                                            |

|                                            |

0x0F00 0x0F01

0x0F02 0x0F03

0x0F04

0x0F05

0x0F06

0x0F07

0x0F08

0x0F09 0x0F0A

0x0F19 0x0F1A 0x0F1B

0x0F1C 0x0F1D

0x0F1E 0x0F1F

0x0F20 0x0F21

0x0F22

0x0F23

0x0F24

0x0F25

0x0F26

0x0F27 0x0F28

0x0F29

0x0F2D 0x0F2E

0x0F2F 0x0F30

0x0F31 0x0F32

0x0F33 0x0F34

0x0F35

0x0F36

0x0F37

0x0F38 0x0F39

0x0F3A 0x0F3B

0x0F3C 0x0F3D

0x0F3E

0x0F43

0x0F53

0x0F54 0x0F55

0x0F56 0x0F57

0x0F58 0x0F59

0x0F73

0x0F74

0x0F75

0x0F76

0x0F77

0x0F78

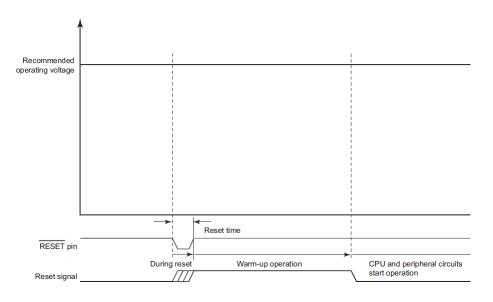

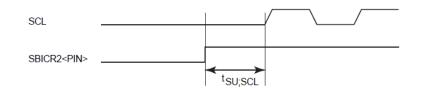

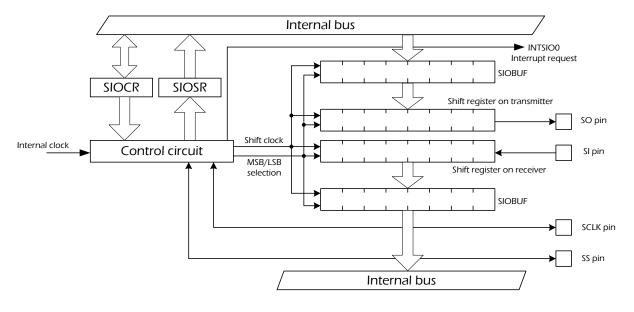

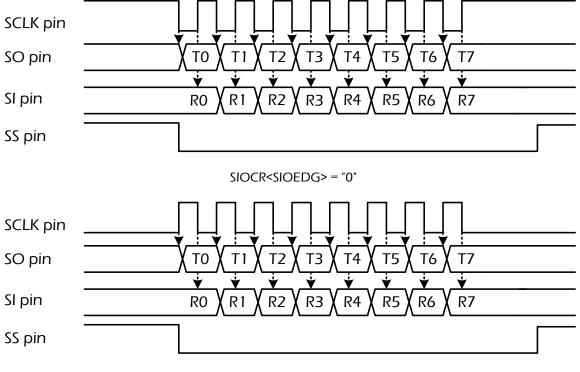

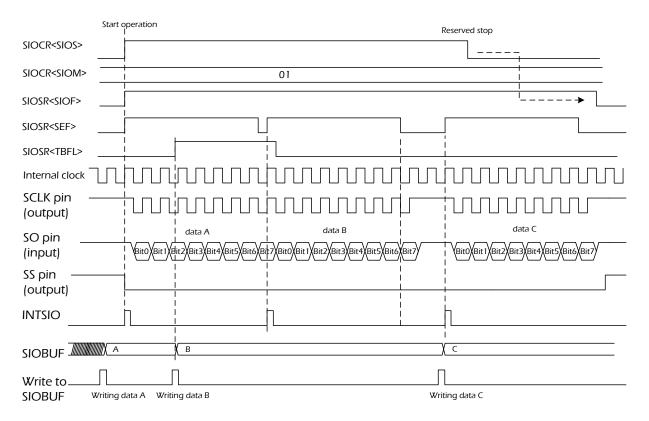

0x0F7F